# Mapping Applications to a Coarse-Grained Reconfigurable Architecture

Yuanqing Guo

#### Composition of the Graduation Committee:

| Prof. Dr. Ir. | Th.    | Krol (promotor), faculty of EEMCS             |

|---------------|--------|-----------------------------------------------|

| Dr. Ir.       | G.J.M. | Smit (assistant-promotor), faculty of EEMCS   |

| Prof. Dr.     | С.     | Hoede, University of Twente, faculty of EEMCS |

| Prof. Dr. Ir. | C.H.   | Slump, University of Twente, faculty of EEMCS |

| Prof. Dr. Ir. | D.     | Verkest, IMEC, Belgium                        |

| Ir.           | J.A.   | Huisken, Silicon Hive, Eindhoven              |

| Prof. Dr. Ir. | Н.     | Corporaal, Technical University of Eindhoven  |

| Prof. Dr. Ir. | A.J.   | Mouthaan, UT, Faculty of EEMCS                |

|               |        | (chairman and secretary)                      |

This research is conducted within the Gecko project (612.064.103) supported by the Dutch organization for Scientific Research NWO.

Group of Computer Architecture, Design & Test for Embedded Systems. P.O. Box 217, 7500 AE Enschede, The Netherlands.

Keywords: mapping and scheduling, instruction generation, compiler, coarse-grained reconfigurable architecture.

Copyright © 2006 by Yuanqing Guo, Enschede, The Netherlands. Email: guoyuanqing@gmail.com

All rights reserved. No part of this book may be reproduced or transmitted, in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage or retrieval system, without the prior written permission of the author.

Printed by Wöhrmann Print Service, Zutphen, The Netherlands. ISBN 90-365-2390-7

# MAPPING APPLICATIONS TO A COARSE-GRAINED RECONFIGURABLE ARCHITECTURE

#### DISSERTATION

to obtain

the doctor's degree at the University of Twente,

on the authority of the rector magnificus,

prof.dr. W.H.M. Zijm,

on account of the decision of the graduation committee,

to be publicly defended

on Friday, September 8th, 2006, at 15.00

by

Yuanqing Guo

born on June 27, 1973 in Beiliu, Chang'an, Shaanxi, China This dissertation is approved by:

Prof. Dr. Ir. Thijs Krol (promotor)

Dr. Ir. Gerard Smit (assistant promotor)

# Acknowledgements

The research presented in this thesis could not have been accomplished without the help and support from many people. I would like to express my sincere gratitude to all of them. Here I would like to mention some of them in particular.

First of all I am very grateful to my assistant promotor, Gerard Smit, for his guidance. Thanks to Gerard, I did not experience the common problem among many Ph.D students: do not know what to do at the very beginning. When I started the project Gerard had many discussions with me to help me to get into the subject. I am also very impressed by his optimism. He always tried to find a direction when I felt "no solution". He suffered a lot from my writing. And on the other hand, I benefited a lot from his comments.

Prof. Thijs Krol is my promotor. With his extensive knowledge on modeling and graph transformation, he helped me a lot in solving the problems that hindered me for a long while by his simple yet clear way of explanation.

I feel so lucky to meet Prof. Cornelis (Kees) Hoede. Kees helped me with the scheduling algorithms. His mathematical background and the way of thinking kept on benefitting me. He taught me the skills of scientific writing. And he helped me to revise my writing. I cannot express my gratitude enough to him for all the help I received from him.

I appreciate Prof. Dr. Hajo Broersma for his supervision on the clustering algorithm. He understood my points even before me!

Paul Heysters is the main designer of the Montium. Unavoidably I asked him many questions and I always received clear answers. My work is most close to that of Michel Rosien's. We had a nice cooperation. And furthermore, he always helped me with C++ and discussed me with my problem. My roommate, Omar Mansour, also had many discussions with me. Many other colleagues in the Chameleon-related projects, Lodewijk Smit, Gerard Rauwerda, Qiwei Zhang, Nikolay Kavaldjiev, Maarten Wiggers, Pas-

cal Wolkotte, Sjoerd Peerlkamp, gave me a lot of help during my work and made the working environment levely.

Seven years ago, Prof. Jack van Lint gave me an opportunity to came to the Netherlands. That opportunity changed my career life a lot. I am very sorry to hear the bad news that he has passed away. I can only keep my appreciation to him in my mind.

I also want to thank Wang Xinmei, my supervisor in Xidian University for my master program and Frans Willems, my supervisor in Technical University of Eindhoven for my MTD program (master of technological design). They guided me in the information theory domain, which is still my favorite subject.

There is life outside the university. Friends are treasures of the lifetime. The parties with Paul Volf, Mortaza Barge, Behnaz and Kimia are always accompanied by lots of fun and laugh. I especially treasure the gatherings that we had together.

I got to know many friends during my stay in Enschede. I can only mention the names of some of them here: Wu Jian, Wang Yu, He Hong, Zhang Dongsheng, Xu Jiang, Liu Fei, Wang Wuyang, Luo Dun, Pei Linlin, Jin Yan, Liang Weifeng, Liu Di, Wu Lixin, Cheng Jieyin, Luo Yiwei, Zhang Junnian.

Last but not least, I want to thank all my family members. My husband (Jianbo Zhang) always supported unconditionally; My son (Andy Zhang) made me understand the real meaning of "love"; My parents give me all the love and help they can offer; My brothers (Guo Baiyi and Guo Baiwei), my sisters in law (Jia Baoying and Yao Na) and my lovely nephew (Guo Tiancheng) are always there when I need them.

Enschede, September 2006 Yuanqing Guo

## Abstract

Today the most commonly used system architectures in data processing can be divided into three categories: general purpose processors, application specific architectures and reconfigurable architectures. General purpose processors are flexible, but inefficient and for some applications do not offer enough performance. Application specific architectures are efficient and give good performance, but are inflexible. Recently reconfigurable systems have drawn increasing attention due to their combination of flexibility and efficiency. Reconfigurable architectures limit their flexibility to a particular algorithm domain. Two types of reconfigurable architectures exist: fine-grained in which the functionality of the hardware is specified at the bit level and coarse-grained in which the functionality of the hardware is specified at the word level. High-level design entry tools are essential for reconfigurable systems, especially coarse-grained reconfigurable architectures. However, the tools for coarse-grained reconfigurable architectures are far from mature.

This thesis proposes a method for mapping applications onto a coarse-grained reconfigurable architecture. This is a heuristic method which tackles this complex problem in four phases: translation, clustering, scheduling and allocation. In this thesis, the Montium tile processor, a coarse-grained reconfigurable architecture, is used to demonstrate the proposed mapping method. In the translation phase, an input program written in a high-level language is translated into a control data flow graph; and some transformations and simplifications are done on the control data flow graph. In the clustering phase, the data flow graph is partitioned into clusters and mapped onto an unbounded number of fully connected Arithmetic Logic Units (ALUs). The ALU structure is the main concern of this phase and we do not take the inter-ALU communication into consideration. In the scheduling phase the graph obtained from the clustering phase is scheduled taking the maximum number of ALUs into account. The scheduling algorithm tries to minimize the num-

ber of clock cycles used for the given application under the constraints of the number of distinct reconfigurations of ALUs. In the allocation phase, variables are allocated to memories or registers, and data moves are scheduled. The main concern in this phase is the details of the target architecture.

There are many constraints and optimization objectives that need to be considered during the mapping and scheduling procedure. According to the above mentioned division only parts of constraints and optimization goals are considered in each phase, which simplifies the problem dramatically. Furthermore, after the division, part of our work relates to the existing research work, especially the work in the clustering and the scheduling phases. This connection is very important because on one hand, we can build our work on the results of others; on the other hand, the result of our work can also be used by others.

Different levels of heuristics are used in the mapping procedure. In our opinion, using a greedy method is the only practical choice because the original mapping task is too complex to be handled in an optimal way. To decrease the negative consequences caused by the sequential order of the heuristics, when tackling each subproblem, we take the requirements of other subproblems also into consideration.

In the Montium, a two-layer decoding technique is used. This technique limits the configuration space to simplify the structure of instruction fetching, which is good for reducing energy consumption and cost. However, the compiler has to face the challenge of decreasing the number of distinct configurations, i.e., generating a limited number of different instructions, which is the most difficult requirement to the Montium compiler. This is also the main difference between the Montium compiler and a compiler for other architectures. However, these constraints have a good reason: they are inherent to energy efficiency, so we believe that it will be used more and more in future energy-efficient computing architectures. Therefore, we have to find ways to cope with these constraints.

To generate only a few different instructions, our approach tries to find the regularity in the algorithms. Therefore, regularity selection algorithms are used (e.g., template selection in the clustering phase, pattern selection in the scheduling phase). These algorithms find the most frequently used templates or patterns in an application. By using these templates or patterns, the number of different instructions is small.

# Samenvatting

De systeem architecturen die vandaag de dag het meest in gebruik zijn, kunnen worden onderverdeeld in drie categorieën: processoren voor algemene doeleinden, architecturen voor specifieke applicaties en herconfigureerbare architecturen. Processoren voor algemene doeleinden zijn flexibel maar niet efficiënt en voor sommige applicaties presteren ze niet genoeg. Architecturen voor specifieke applicaties zijn efficiënt en presteren goed maar zijn niet flexibel. De laatste tijd krijgen herconfigureerbare systemen steeds meer aandacht vanwege de combinatie van efficiëntie en flexibiliteit. Herconfigureerbare architecturen beperken hun flexibiliteit tot een bepaald algorithme domein. Er bestaan twee soorten herconfigureerbare architecturen: fijn-mazig, waar de functionaliteit is gespecificeerd op bit niveau en grof-mazig, waar de functionaliteit is gespecificeerd op woord niveau. Goede software ondersteuning voor het ontwerpen op hoog abstractie niveau is essentieel voor herconfigureerbare systemen, in het bijzonder grof-mazige herconfigureerbare architecturen. Echter, de software ondersteuning voor grof-mazige herconfigureerbare architecturen zijn verre van volwassen.

Dit proefschrift stelt een methode voor om applicaties op een grof-mazige herconfigureerbare architectuur af te beelden. Dit is een op heuristieken gebaseerde methode die dit probleem probeert op te lossen in vier fases: vertaling, groeperen, plannen en allocatie. In dit proefschrift wordt de Montium tile processor, een grof-mazige herconfigureerbare architectuur, gebruikt om de voorgestelde afbeelding te demonstreren. In de vertalingfase wordt een invoer programma, geschreven in een hoog niveau programmeertaal, vertaald in een "Control Data Flow" graaf. Op die graaf worden dan een aantal transformaties en simplificaties uitgevoerd. In de groeperingfase wordt de graaf gepartitioneerd in groepen en afgebeeld op een onbegrensd aantal volledig verbonden "Arithmetic Logic Units (ALUs)". De ALU structuur is het hoofd doel van deze fase. We houden geen rekening met communi-

catie tussen de ALUs in deze fase. In de planningfase word de graaf, die verkregen is uit de groepering fase, ingepland, rekening houdend met het maximale aantal ALUs. Het planningalgorithme probeert het aantal klok cycles voor een gegeven applicatie te minimaliseren, rekening houdend met de beperkingen die worden opgelegd door het beperkt aantal herconfiguraties die mogelijk zijn per ALU per applicatie. In de allocatie fase worden variabelen toegewezen aan geheugens of registers en data transporten worden ingepland. De hoofdzaak in deze fase zijn de details van de doel architectuur.

Er zijn veel beperkingen en optimalisatie doelen die in overweging moeten worden genomen tijdens het afbeelden en inplannen. Volgens de onderverdeling die hierboven is genoemd worden in elke fase slechts een deel van de beperkingen bekeken. Dit simplificeert het probleem enorm. Tevens, na de onderverdeling kan een deel van ons werk gerelateerd worden aan eerder onderzoek, in het bijzonder de groepering en planning fases. Dit is erg belangrijk omdat we ons onderzoek dus kunnen baseren op het werk van anderen en anderen ons werk kunnen gebruiken in hun onderzoek.

Verschillende niveaus van heuristiek worden gebruikt tijdens de afbeelding. Volgens ons is een "greedy" methode de enige practische keuze omdat de oorspronkelijke afbeelding te complex is om een optimale oplossing te vinden. Om de negatieve consequenties, veroorzaakt door de sequentiële volgorde van de heuristieken tijdens het oplossen van elk sub-probleem, te verminderen, nemen we de eisen en beperkingen van andere sub-problemen ook in overweging.

In de Montium wordt een twee-laags decoderingstechniek gebruikt. Deze techniek beperkt de configuratieruimte om de structuur van het ophalen van instructies te simplificeren. Dit is goed om het energie verbruik en de kosten te reduceren. Echter, de compiler heeft dan het probleem om het aantal verschillende configuraties te verminderen, d.w.z., om een beperkt aantal verschillende configuraties te genereren. Dit is de moeilijkste eis waar de Montium Compiler aan moet voldoen. Dit is ook het grootste verschil tussen de Montium Compiler en een compiler voor andere architecturen. Deze beperkingen hebben echter een goede reden, ze zijn inherent aan energie efficiëntie. Wij geloven dus dat het in de toekomst meer en meer gebruikt zal worden in toekomstige energie efficiënte architecturen. Daarom moeten we een manier vinden om met deze beperkingen te kunnen werken.

Om het voor elkaar te krijgen om een beperkt aantal verschillende instructies te genereren, is onze aanpak het zoeken van de regelmaat in algorithmes door middel van algorithmes die selecteren op basis van regelmaat (b.v. template selectie in de groeperingfase, patroon selectie in de planningfase). Deze algorithmes vinden de meest gebruikte patronen en templates in een applicatie. Door het gebruik van deze templates en patronen is het aantal verschillende instructies klein.

# Table of Contents

| $\mathbf{A}$ | ckno  | wledgements                                                      | $\mathbf{v}$ |

|--------------|-------|------------------------------------------------------------------|--------------|

| $\mathbf{A}$ | bstra | act                                                              | vii          |

| Sa           | amen  | vatting                                                          | ix           |

| 1            | Inti  | roduction                                                        | 1            |

|              | 1.1   | Reconfigurable architectures                                     | 1            |

|              | 1.2   | Design automation                                                | 2            |

|              | 1.3   | Chameleon system-on-chip                                         | 3            |

|              | 1.4   | Montium tile processor                                           | 4            |

|              | 1.5   | A compiler for coarse-grained reconfigurable systems             | 5            |

|              | 1.6   | Contributions of this thesis                                     | 6            |

|              | 1.7   | Organization of this thesis                                      | 7            |

| 2            | Coa   | arse-grained reconfigurable architectures                        | 9            |

|              | 2.1   | Introduction                                                     | 9            |

|              | 2.2   | General purpose processor                                        | 10           |

|              | 2.3   | Application specific integrated circuit                          | 11           |

|              | 2.4   | Reconfigurable hardware                                          | 12           |

|              | 2.5   | Select overview of coarse-grained reconfigurable architectures . | 13           |

|              |       | 2.5.1 The Pleiades architecture                                  | 13           |

|              |       | 2.5.2 Silicon Hive's reconfigurable accelerators                 | 14           |

|              |       | 2.5.3 The MorphoSys reconfigurable processor                     | 15           |

|              |       | 2.5.4 PACT's extreme processor platform                          | 16           |

|              |       | 2.5.5 Montium tile processor                                     | 17           |

|              |       | 2.5.6 Summary                                                    | 21           |

|              | 2.6   | Conclusion                                                       | 22           |

#### Table of Contents

| 3                   | The        | e framework of a compiler for a coarse-grained reconfig-        |    |

|---------------------|------------|-----------------------------------------------------------------|----|

| urable architecture |            |                                                                 | 23 |

|                     | 3.1        | Introduction                                                    | 24 |

|                     | 3.2        | Overview of mapping methods                                     | 24 |

|                     |            | 3.2.1 Mapping techniques for clustered                          |    |

|                     |            | micro-architectures                                             | 24 |

|                     |            | 3.2.2 Compiling for coarse-grained reconfigurable architectures | 25 |

|                     |            | 3.2.3 Summary                                                   | 27 |

|                     | 3.3        | A sample architecture                                           | 28 |

|                     | 3.4        | Challenges of designing a Montium compiler                      | 29 |

|                     |            | 3.4.1 Optimization goals                                        | 29 |

|                     |            | 3.4.2 Constraints                                               | 30 |

|                     |            | 3.4.3 Configuration space                                       | 31 |

|                     |            | 3.4.4 Tasks of a Montium compiler                               | 35 |

|                     | 3.5        | Mapping procedure                                               | 35 |

|                     | 3.6        | Conclusion                                                      | 42 |

| 4                   | Tra        | nslation and transformation                                     | 43 |

| •                   | 4.1        | Definition of Control Data Flow Graphs                          | 44 |

|                     | 4.2        | Information extraction and transformation                       | 53 |

|                     | 1          | 4.2.1 Finding arrays                                            | 53 |

|                     |            | 4.2.2 New value representation                                  | 55 |

|                     |            | 4.2.3 Separating state space                                    | 57 |

|                     |            | 4.2.4 Finding loops:                                            | 58 |

|                     | 4.3        | Data flow graph                                                 | 60 |

|                     | 4.4        | Related work                                                    | 62 |

|                     | 4.5        | Conclusion and discussion                                       | 64 |

| _                   | Α -        | landaria a almadidhaa                                           | CF |

| 5                   |            | lustering algorithm                                             | 65 |

|                     | 5.1        |                                                                 | 66 |

|                     | 5.2        | Template Generation and Selection Algorithms                    | 70 |

|                     |            | 5.2.1 The Template Generation Algorithm                         | 72 |

|                     | <b>-</b> 0 | 5.2.2 The Template Selection Algorithm                          | 79 |

|                     | 5.3        | Experiments                                                     | 84 |

|                     | 5.4        | Introducing cluster nodes in DFG                                | 85 |

|                     | 5.5        | Overview of related work                                        | 87 |

|                     | 5.6        | Conclusion and future work                                      | 88 |

#### TABLE OF CONTENTS

| 6 | Sche | eduling of clusters 91                                             |

|---|------|--------------------------------------------------------------------|

|   | 6.1  | Definition                                                         |

|   | 6.2  | Problem description                                                |

|   | 6.3  | A multi-pattern scheduling algorithm                               |

|   |      | 6.3.1 Algorithm description                                        |

|   |      | 6.3.2 Example                                                      |

|   |      | 6.3.3 Complexity comparison with fixed-pattern list scheduling 104 |

|   |      | 6.3.4 Experiment                                                   |

|   | 6.4  | Pattern selection                                                  |

|   |      | 6.4.1 Pattern generation                                           |

|   |      | 6.4.2 Pattern selection                                            |

|   |      | 6.4.3 Experiment                                                   |

|   |      | 6.4.4 Discussions                                                  |

|   | 6.5  | A column arrangement algorithm                                     |

|   |      | 6.5.1 Lower bound                                                  |

|   |      | 6.5.2 Algorithm description                                        |

|   |      | 6.5.3 Computational complexity                                     |

|   |      | 6.5.4 Experiment                                                   |

|   | 6.6  | Using the scheduling algorithm on CDFGs                            |

|   | 6.7  | Related work                                                       |

|   | 6.8  | Conclusions                                                        |

| 7 | Rese | ource allocation 129                                               |

|   | 7.1  | Introduction                                                       |

|   | 7.2  | Definitions                                                        |

|   | 7.3  | Allocating variables                                               |

|   |      | 7.3.1 Source-destination table                                     |

|   |      | 7.3.2 Algorithm for allocating variables and arrays 139            |

|   |      | 7.3.3 Ordering variables and arrays for allocating 139             |

|   |      | 7.3.4 Priority function                                            |

|   | 7.4  | Scheduling data moves                                              |

|   |      | 7.4.1 Determining the order of moves                               |

|   |      | 7.4.2 Optimization                                                 |

|   |      | 7.4.3 Spilling STLRs                                               |

|   | 7.5  | Modeling of crossbar allocation, register allocation and mem-      |

|   |      | ory allocation                                                     |

|   |      | 7.5.1 Crossbar allocation                                          |

|   |      | 7.5.2 Register arrangement                                         |

#### Table of Contents

|   |              | 7.5.3 Memory arrangement        | 153 |  |  |  |  |

|---|--------------|---------------------------------|-----|--|--|--|--|

|   | 7.6          | Related work                    | 153 |  |  |  |  |

|   | 7.7          | Conclusion                      | 154 |  |  |  |  |

| 8 | Con          | nclusions                       | 157 |  |  |  |  |

|   | 8.1          | Summary                         | 157 |  |  |  |  |

|   | 8.2          | Lessons learned and future work | 159 |  |  |  |  |

| B | ibliog       | graphy                          | 161 |  |  |  |  |

| P | Publications |                                 |     |  |  |  |  |

# Chapter 1

## Introduction

Reconfigurable computing has been gaining more and more attention over the last decade. To automate the application design flow for coarse-grained reconfigurable systems, the CADTES group at the University of Twente is designing a compiler for such systems. The procedure of mapping computationally intensive tasks to coarse-grained reconfigurable systems is the key part in the compiler, which is the topic of this thesis.

## 1.1 Reconfigurable architectures

A computer system executes user programs and solves user problems. The most commonly used computer architectures in data processing can be divided into three categories: general purpose processors, application-specific integrated circuits and reconfigurable architectures.

In this thesis, by *performance* of a processor, we mean the amount of clock cycles it takes to run a specific application program under certain specified

conditions; *flexibility* refers to the programmability of the system; *energy-efficiency* refers to the relative energy it takes to perform a certain program on a certain architecture.

The designs of these architectures make different tradeoffs between flexibility, performance and energy-efficiency. General purpose processors are flexible, but inefficient and offer relatively poor performance, whereas application specific architectures are efficient and give good performance, but are inflexible. Reconfigurable architectures make a tradeoff between these two extremes thereby limiting their flexibility to a particular algorithm domain. Two types of reconfigurable architectures exist: coarse-grained and fine-grained. In fine-grained reconfigurable architectures, such as Field Programmable Gate Arrays (FPGAs), the functionality of the hardware is specified at the bit level. Therefore, they are efficient for bit-level algorithms. However, word-level algorithms are more suitable for coarse-grained reconfigurable architectures. Coarse-grained reconfigurable elements also provide an energy advantage over fine-grained reconfigurable elements because the control part is small.

To compete with application specific architectures, which are notorious for their long design cycles, high-level design entry tools are needed for reconfigurable architectures. Without proper tools, developing these architectures is a waste of time and money. In recent years, a number of companies that developed reconfigurable systems have gone bankrupt (e.g., Chameleon systems [80] [86], Quicksilver [42]) because they designed systems without proper development tools.

## 1.2 Design automation

In a computer system, the hardware provides the basic computing resources. The applications define the way in which these resources are used to solve the computing problems. Tools act as bridges between hardware resources and applications. According to the abstraction level of the source language, tools are divided into low-level design entry tools and high-level design entry tools. Low-level design entry tools such as Hardware Description Languages (HDLs) and assemblers require the programmer to have a thorough understanding of the underlying hardware organization. The programmer has a long learning curve before he or she is experienced enough to exploit all the features of the architecture. The design effort and costs are high and the design cycle

is long. High-level design entry languages (e.g., C or MATLAB) provide an abstraction of the underlying hardware organization. Two main advantages of a high-level design entry tool are:

- Architecture independent application. With the help of such tools, application engineers can create algorithms without being an expert on the underlying hardware architectures. This makes it possible for application engineers to focus on the algorithms instead of on a particular architecture. This also reduces the design cycle of new applications considerably and saves engineering costs.

- Automatic exploitation of the desirable features (such as parallelism) of the hardware architectures. Specifications of algorithms are often provided in a sequential high-level language. Human beings are accustomed to thinking sequentially and have difficulty in extracting the maximum amount of parallelism achievable on a specific architecture from a sequential description. Good high-level design entry tools automatically manage the allocation of low level hardware, and allow the resources to cooperate in the best way.

High-level design entry tools for general purpose processors have been studied for a long time and the techniques are already very mature, giving general purpose processors strong support. Although high-level design entry tools are essential for reconfigurable systems, especially coarse-grained reconfigurable architectures, the tools for these architectures are far from mature.

## 1.3 Chameleon system-on-chip

The application domain of our research is energy-efficient mobile computing, e.g., multi-standard communicators or mobile multimedia players. A key challenge in mobile computing is that many attributes of the environment vary dynamically. For example, mobile devices operate in a dynamically changing environment and must be able to adapt to each new environment. A mobile computer will have to deal with unpredictable network outages and be able to switch to a different network without changing the application. Therefore, it should have the flexibility to handle a variety of multimedia services and standards (such as different communication protocols or video

decompression schemes) and the ability to adapt to the nomadic environment and available resources. As more and more these applications are added to mobile computing, devices need more processing power. Therefore, performance is another important requirement for mobile computing. Furthermore, a handheld device should be able to find its place in a user's pocket. Therefore, its size should be small enough. Finally, for compelling business reasons, extending the time between battery recharges has long been one of the highest priorities in the design of mobile devices. This implies a need for ultra-low energy consumption. To summarize: computer architectures for mobile computing should be flexible, with high performance and high energy-efficiency.

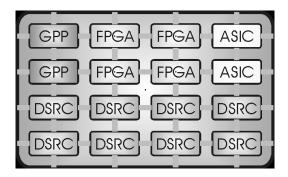

The Chameleon System-on-Chip (SoC) [43][82] is a heterogeneous reconfigurable SoC designed for mobile applications. Such a SoC consists of several tiles (e.g., 16 tiles). These tiles can be heterogeneous, for example, general-purpose processors (such as ARM cores), bit-level reconfigurable parts (such as FPGAs), word-level reconfigurable parts (such as Montium tiles described in detail later), general Digital Signal Processors (DSPs) or some application-specific integrated circuits (such as a Turbo-decoder). This tile-based architecture combines the advantages of all types of architectures by mapping application tasks (or kernels) onto the most suitable processing entity. We believe that the efficiency (in terms of performance and energy) of the system can be improved significantly by a flexible mapping of processes to processing entities [84].

The Chameleon SoC design concentrates on streaming applications. Examples of these applications are video compression (discrete cosine transforms, motion estimation), graphics and image processing, data encryption, error correction and demodulation, which are the key techniques in mobile computing.

#### 1.4 Montium tile processor

As an example in this section, the Montium tile processor, a coarse-grained reconfigurable architecture designed by the Computer Architecture Design and Test for Embedded Systems (CADTES) group at the University of Twente [43][82], is described. The Montium is used throughout this thesis as an example of a coarse-grained building block. The Montium tile is characterized by its coarse-grained reconfigurability, high performance and

low energy consumption. The Montium achieves flexibility through reconfigurability. High performance is achieved by parallelism, because the Montium has several parallel processing elements. Energy-efficiency is achieved by the locality of reference which means data are stored close to the processing part that uses them. It costs considerably less energy for a processing part to access the data stored in an on-tile storage location compared to the access of data from off-chip memory. The Montium tiles allow different levels of storage: local register, local memory, global memory and global register. This allows several levels of locality of reference. More details about the Montium structure can be found in Chapter 2.

A new technique that is used extensively in the Montium tile design is the two-layer decoding method (see Chapter 3). This method limits configuration spaces to simplify the instruction fetch part, which is good for energy consumption and cost. The disadvantage incurred by this technique is the limited flexibility. However, the Montium does not aim to provide a general purpose hardware for all types of complex algorithms found in conventional microprocessors. Instead, the Montium is designed for DSP-like algorithms found in mobile applications. Such algorithms are usually regular and have high computational density.

## 1.5 A compiler for coarse-grained reconfigurable systems

The philosophy of the design of a coarse-grained reconfigurable system is to keep the hardware simple and let the compiler bear more responsibilities. However, it is not an easy task to use all the desirable characteristics of a coarse-grained reconfigurable architecture. If those characteristics are not used properly, the advantages of an architecture might become its disadvantages. Therefore, a strong compiling support designed alongside the work of the hardware design is a necessity.

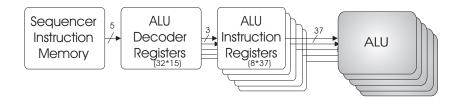

There are many other compilers for coarse-grained reconfigurable architectures described in literatures, which will be introduced in Chapter 3. The most remarkable point that distinguishes our work from the other compilers for coarse-grained reconfigurable architectures is that we limited the size of configuration spaces for energy-efficiency. In most microprocessors, instructions are stored in an instruction memory. At run time, instructions

are fetched and decoded, and fed to all components. In the Montium, instructions for each component are stored in a local-configuration memory. A sequencer acts as a state machine to choose the instructions for each component. Therefore, the number of different instructions is limited by both the size of sequencer-instruction memory and the size of local-configuration memory. This property can be summarized in an easily-understood sentence: "we prefer the same instructions to be executed repeatedly rather than many different instructions to be executed once." This instruction fetching technique is very energy-efficient and, we believe, it will be used more and more in future computing architectures. Therefore, new mapping techniques that can handle constraints of the configuration space are being investigated.

This thesis is about the compiler for a coarse-grained reconfigurable architecture. The Montium tile processor is used as a sample architecture. This thesis concentrates on mapping an application program written in a high level language (C++ or Matlab) to a coarse-grained reconfigurable processing tile within the constraints of the configuration space. It focuses on decreasing the number of clock cycles under all the constraints of the processor structure.

#### 1.6 Contributions of this thesis

The major contributions of this thesis can be summarized as follows:

- Mapping and scheduling framework: The framework for the mapping applications to a coarse-grained reconfigurable architecture is proposed. It has four phases: Translation, clustering, scheduling and allocation.

- Data value representation: The presented new data value representation is very convenient for generating AGU instructions.

- Template generation algorithm: We present a template generation which can generate all the connected templates and finding all the matches in a given graph. The shape of templates is not limited as in the previous work. The algorithm can be used in application-specific integrated circuit design or generating CLBs in FPGAs.

- Template selection algorithm: The template selection algorithm presented choose the generated templates to cover a graph, which min-

imizes the number of distinct templates that are used as well as the number of instances of each template.

- Color-constrained scheduling: The scheduling problem for the Montium is modeled as a color-constrained scheduling problem. A three-step approach for color-constrained scheduling problem is proposed.

- Multi-pattern list scheduling algorithm: A modified version of the traditional list scheduling algorithm is presented. The modified algorithm schedules the nodes of a graph using a set of given patterns.

- Pattern selection algorithm: The algorithm finds the most frequently occurring patterns in a graph. By using these selected patterns, the multi-pattern list scheduling can schedule a graph using fewer clock cycles.

- Column arrangement algorithm: This algorithm is developed to decrease the number of one-ALU configurations of each ALU.

- Resource allocation approach: The procedure of resource allocation is presented.

- Modeling of the crossbar allocation, register allocation, memory allocation problems: The crossbar allocation, register allocation, memory allocation problems are modeled.

## 1.7 Organization of this thesis

The rest of this thesis is organized as follows:

- Chapter 2 presents coarse-grained reconfigurable architectures and in particular, the structure of the Montium tile processor architecture, which is the sample architecture of the mapping work described in this thesis.

- Chapter 3 gives an overview of other work related to the compilers for coarse-grained reconfigurable architectures. Further, the challenges of the mapping problem for coarse-grained reconfigurable architectures are discussed. The framework of our four-phase approach consists of transformation, clustering, scheduling and allocation.

#### CHAPTER 1: INTRODUCTION

- Chapter 4 presents the translation and transformation phase. In this phase, an input C program is first translated into a control data flow graph. After that some transformations and simplifications are performed on the control data flow graph.

- Chapter 5 presents the clustering phase. In this phase, the primitive operations of a data flow graph are partitioned into clusters and mapped to an unbounded number of fully connected ALUs.

- Chapter 6 presents the scheduling algorithm, which schedules the clusters within the constraint of the configuration space.

- Chapter 7 presents the allocation algorithm, which focuses on the details of the Montium structure. Two mains jobs executed during the allocation phase are the allocation of variables and the arrangement of communications.

- Chapter 8 summarizes the thesis and presents the final conclusions.

# Chapter 2

# Coarse-grained reconfigurable architectures

This chapter presents the commonly used computer architectures: general-purpose processor, application specific integrated circuits and reconfigurable architectures. Reconfigurable architectures can be divided into two groups: finegrained and coarse-grained. The advantages and disadvantages of these architectures are discussed. Coarse-grained reconfigurable architectures are the focus of the chapter. Several sample architectures are described.

#### 2.1 Introduction

A computer system has many hardware resources that may be required to solve a problem: arithmetic and logic units, storage space, input/output devices, etc. The most commonly used computer system architectures in data

processing can be divided into three categories: general purpose processors, application specific architectures and coarse-grained reconfigurable architectures.

## 2.2 General purpose processor

General-purpose computers have served us well over the past couple of decades. The architecture of a general purpose processor is widely studied, and many optimizations of processor performance have been done. Current general purpose Central Processing Units (CPUs) are many orders of magnitude more powerful than the first ones. They are also the most flexible hardware architectures. Simply by writing the right software, an application programmer can map a large set of applications on general purpose processor hardware. Moreover, tooling support for general-purpose processors has been researched for a long period and many mature tools are now available. Compared with other architectures, general purpose processors are easier to program. The application design procedure is also faster and cheaper.

All general purpose processors rely on the von Neumann instruction fetchand-execute model. Although general purpose processors can be programmed to perform virtually any computational task, with the von Neumann model, they have to pay for this flexibility with a high energy consumption and significant overhead of fetching, decoding and executing a stream of instructions on complex general purpose data paths. The model has some significant drawbacks. Firstly, the energy overhead due to its programmability most often dominates the energy dissipation of the intended computation. Every single computational step, (e.g., addition of two numbers), requires fetching and decoding an instruction from the instruction memory, accessing the required operands from the data memory, and executing the specified computation on a general-purpose functional unit. Secondly, the clock speed of processors has grown much faster than the speed of the memory. Therefore, sequential fetching of every control instruction from the memory hampers the performance of the function unit. The gap between memory access speed and processor speed is known as the von Neumann bottleneck. Some techniques, such as using cashes or separating instruction and data memories, have been used to relieve the von Neumann bottleneck. However, these efforts are not sufficient for mobile applications where the computational density is very high. Thirdly, to achieve high performance, a general-purpose processor must run at a high clock frequency; therefore, the supply voltage cannot be aggressively reduced to save energy. Finally, although the execution speed of general purpose processors has been increased many times over the last decades, it has, as a general rule, led to inefficiency compared to an application specific implementation of a particular algorithm. The reason is that many optimizations in general purpose processors are for general cases but not for a specific algorithm.

A digital signal processor is a processor optimized for digital signal processing algorithms. We consider it as a general purpose processor because it still uses the von Neumann model. The need of fetching every single instruction from memory and decoding it brings also in these processors a considerable amount of power consumption overhead.

## 2.3 Application specific integrated circuit

An application specific integrated circuit, as opposed to a general purpose processor, is a circuit designed for a specific application rather than general use. The goal of application specific modules is to optimize the overall performance by only focusing on their dedicated use. Also due to the applicationoriented design goal, the application specific integrated circuit presents the most effective way of reducing energy consumption and has shown to lead to huge power savings. Performing complex multimedia data processing functions in dedicated hardware, optimized for energy-efficient operation, reduces the energy per operation by several orders of magnitude compared with a software implementation on a general purpose processor. Furthermore, for a specific use, an application-specific integrated circuit has lower chip area costs compared to a general purpose processor. However, the disadvantage of dedicated hardware is the lack of flexibility and programmability. Their functionality is restricted to the capabilities of the hardware. For each new application, the hardware has to be redesigned and built. The technological challenges in the design of custom application specific architectures are usually significantly smaller than the design of general purpose circuits. This may compensate for the disadvantages in some applications. However, the smaller flexibility, and consequently the fact that a new chip design is needed for even the smallest change in functionality, is still the fatal shortcoming of application specific integrated circuits.

## 2.4 Reconfigurable hardware

An application specific architecture solution is too rigid, and a general purpose processor solution is too inefficient. Neither general purpose processors nor application specific architectures are capable of satisfying the power and flexibility requirements of future mobile devices. Instead, we want to make the machine fit the algorithm, as opposed to making the algorithm fit the machine. This is the area of reconfigurable computing systems.

Reconfigurable hardware is ideal for use in System-on-Chips (SoCs) as it executes applications efficiently, and yet maintains a level of flexibility not available with more traditional full custom circuitry. This flexibility allows for both hardware reuse and post fabrication modification. Hardware reuse allows a single reconfigurable architecture to implement many potential applications, rather than requiring a separate custom circuit for each. Furthermore, post-fabrication modification allows for alterations in the target applications, bug-fixes, and reuse of the SoC across multiple similar deployments to amortize design costs. Unlike microprocessors in which functionality is programmable through 'instructions', reconfigurable hardware changes its functionality within its application domain through 'configuration bits', which means the programmability is lower than that of a general purpose processor.

Fine-grained: Reconfigurable processors have been widely associated with Field Programmable Gate Array (FPGA)-based system designs. An FPGA consists of a matrix of programmable logic cells with a grid of interconnecting lines running between them. In addition, there are I/O pins on the perimeter that provide an interface between the FPGA, the interconnecting lines and the chip's external pins. However, FPGAs tend to be somewhat fine-grained in order to achieve a high degree of flexibility. This flexibility has its place for situations where the computational requirements are either not known in advance or vary considerably among the needed applications. However, in many cases this extreme level of flexibility is unnecessary and would result in significant overheads of area, delay and power consumption.

Coarse-grained: Contrasted with FPGAs, the data-path width of coarse-grained reconfigurable architectures is more than one bit. Over the last 15 years, many projects have investigated and successfully built systems where

the reconfiguration is coarse-grained and is performed within a processor or amongst processors [39] [40]. In such systems the reconfigurable unit is a specialized hardware architecture that supports logic reconfiguration. The reconfiguration procedure is much faster than that found in FPGAs. Because the application domain is known, full custom data paths could be designed, which are drastically more area-efficient.

# 2.5 Select overview of coarse-grained reconfigurable architectures

Many coarse-grained reconfigurable architectures have been developed over the last decades. Here a selected overview is given. For a more comprehensive overview of reconfigurable architectures, we refer to [15] and [39].

#### 2.5.1 The Pleiades architecture

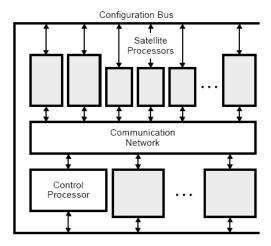

Figure 2.1: The Pleiades Architecture Template

The Pleiades architecture was designed by the University of California at Berkeley for digital signal processing algorithms [1] [75] [76]. The architecture is centered around a reconfigurable communication network (see Figure 2.1). Connected to the network are a control processor that is a general-purpose

microprocessor core, and an array of heterogeneous autonomous processing elements called satellite processors. The satellites can be fixed components or reconfigurable data paths. The control processor configures the available satellite processors and the communication network at run-time to construct the dataflow graph corresponding to a given computational kernel directly in the hardware.

The dominant, energy-intensive computational kernels of a given DSP algorithm are implemented on the satellite processors as a set of independent, concurrent threads of computation. The remainder of the algorithm, which is not compute-intensive, is executed on the control processor.

#### 2.5.2 Silicon Hive's reconfigurable accelerators

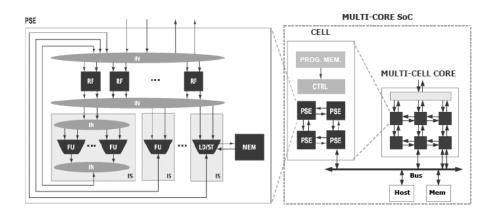

Figure 2.2: Hierarchy of Silicon Hive's Processor Cell Template

The Silicon Hive processor cell template is a hierarchical structure (see Figure 2.2) [13] [37]. A core consists of multiple cells, each of which has its own thread of control. A cell has a VLIW-like controller (CTRL), a configuration memory and multiple Processing and Storage Elements (PSEs). Cells can have streaming interfaces, which allow the cells to be interconnected. For scalability reasons, usually a nearest-neighbor interconnect strategy is chosen, leading to a mesh structure. PSEs consist of register files and issue slots. Issue slots consist of interconnect networks and function units.

A cell is a fully-operational processor capable of computing complete algorithms. A cell typically executes one algorithm at a time.

#### 2.5.3 The MorphoSys reconfigurable processor

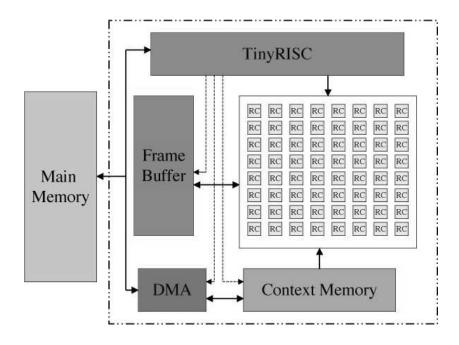

Figure 2.3: The architecture of MorphoSys systems

The MorphoSys reconfigurable processor was developed by researchers in the University of California, targeted at applications with inherent data-parallelism, high regularity and high throughput requirements. The MorphoSys architecture, shown in Figure 2.3, comprises an array of Reconfigurable Cells (RC Array) with configuration memory (Context Memory), a control processor (TinyRISC), data buffer (Frame Buffer) and DMA controller. The main component of MorphoSys is the 8 x 8 RC array. Each RC has an ALU-multiplier, a register file and is configured through a 32-bit context word. The RC Array is dedicated to the exploitation of parallelism available in an applications algorithm. The tiny RISC handles serial operations, initiates data transfers and controls operation of the RC array. The Frame Buffer enables stream-lined data transfers between the RC Array and main memory, by overlap of computation with data loading and storing.

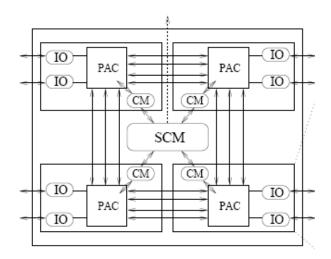

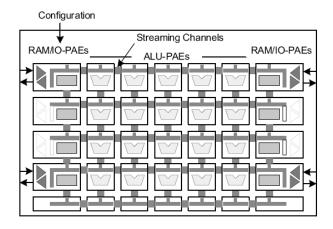

Figure 2.4: XPP device

#### 2.5.4 PACT's extreme processor platform

The eXtreme Processing Platform (XPP) [7] [69] of PACT is a data processing architecture based on an array of coarse-grained, adaptive computing elements called Processing Array Elements (PAEs) and a packet-oriented communication network.

An XPP device contains one or several Processing Array Clusters (PACs) (see Figure 2.4). Each PAC is a rectangular array of PAEs, attached to a control manager responsible for writing configuration data into the PAEs (see Figure 2.5). PAEs can be configured rapidly in parallel while neighboring PAEs are processing data. Entire applications can be configured and run independently on different parts of the array. A PAE is a template for either an ALU named ALU-PAE or for a memory named RAM-PAE. Those in the center of the array are ALU-PAEs, and those at the left and right side are RAM-PAEs with I/O.

A flow graph of an algorithm can be mapped onto a PAC in a natural way. The nodes of the data flow graph are mapped on the PAEs and the edges are mapped on the data network.

Figure 2.5: Structure of a sample XPP Core

#### 2.5.5 Montium tile processor

The Montium tile processor is being designed at the University of Twente. We will describe the Montium tile processor in more detail than other architectures because it functions as the sample architecture of our compiler. The Montium tile is acting as a tile in the Chameleon system-on-chip, which is especially designed for mobile computing.

#### Chameleon System-on-Chip

Figure 2.6: Chameleon heterogeneous SoC architecture

In the Chameleon project we are designing a heterogeneous reconfigurable

SoC [82] (see Figure 2.6). This SoC contains a general purpose processor (e.g. ARM core), a bit-level reconfigurable part (e.g., FPGA) and several word-level reconfigurable parts (e.g., Montium tiles).

We believe that in the future 3G/4G terminals, heterogeneous reconfigurable architectures are needed. The main reason is that the efficiency (in terms of performance or energy) of the system can be improved significantly by mapping application tasks (or kernels) onto the most suitable processing entity. The design of the above-mentioned architecture is useless without a proper tool chain supported by a solid design methodology. At various levels of abstraction, modern computing systems are defined in terms of processes and communication (or synchronization) between processes. These processes can be executed on various platforms (e.g., general purpose CPU, Montium, FPGA, etc). In this thesis we will concentrate on the tools for mapping one such process onto a coarse-grained reconfigurable processing tile (Montium). However, the presented algorithms can also be used for programming FPGAs or other coarse-grained architectures.

#### Montium Architecture

The design of the Montium focuses on:

- Keeping each processing part small to maximize the number of processing parts that can fit on a chip;

- Providing sufficient flexibility:

- Low energy consumption;

- Exploiting the maximum amount of parallelism;

- A strong support tool for Montium-based applications.

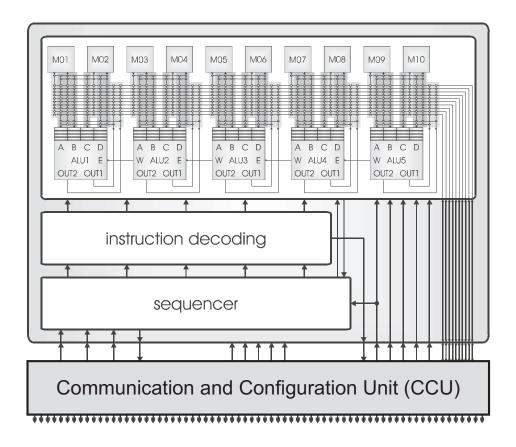

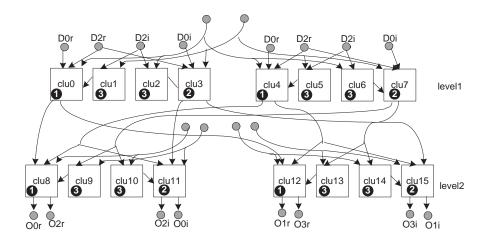

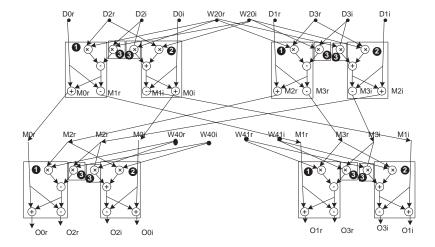

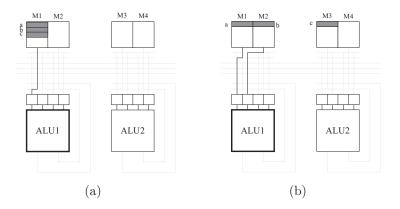

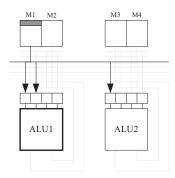

In this section we give a brief overview of the Montium architecture [43]. Figure 2.7 depicts a single Montium processor tile. The hardware organization within a tile is very regular and resembles a very long instruction word architecture. The five identical arithmetic and logic units (ALU1 $\cdots$ ALU5) in a tile can exploit spatial concurrency to enhance performance. This parallelism demands a very high memory bandwidth, which is obtained by having 10 local memories (M01 $\cdots$ M10) in parallel. The small local memories are also motivated by the locality of reference principle. The Arithmetic and

Figure 2.7: Montium processor tile

Logic Unit (ALU) input registers provide an even more local level of storage. Locality of reference is one of the guiding principles applied to obtain energy-efficiency within the Montium. A vertical segment that contains one ALU together with its associated input register files, a part of the interconnect and two local memories is called a Processing Part (PP). The five processing parts together are called the processing part array. A relatively simple sequencer controls the entire processing part array. The Communication and Configuration Unit (CCU) implements the interface with the world outside the tile. The Montium has a datapath width of 16-bits and supports both integer and fixed-point arithmetic. Each local static random access memory

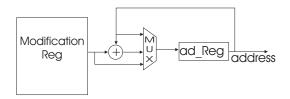

is 16-bit wide and has a depth of 512 positions. Because a processing part contains two memories, this adds up to a storage capacity of 16 Kbit per local memory. A memory has only a single address port that is used for either reading or writing. A reconfigurable Address Generation Unit (AGU) accompanies each memory. The AGU contains an address register that can be modified using base and modification registers.

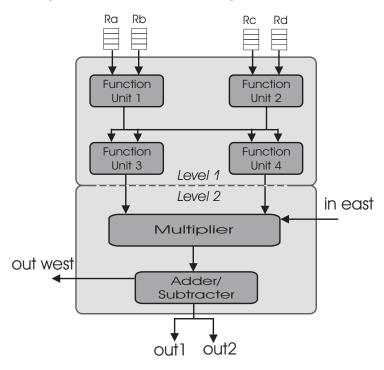

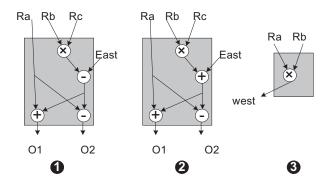

Figure 2.8: Montium ALU

It is also possible to use the memory as a lookup table for complicated functions that cannot be calculated using an ALU, such as sine or division (with one constant). A memory can be used for both integer and fixed-point lookups. The interconnect provides flexible routing within a tile. The configuration of the interconnect can change every clock cycle. There are ten buses that are used for inter-processing part array communication. Note that the span of these buses is only the processing part array within a single tile. The CCU is also connected to the global buses. The CCU uses the global buses to access the local memories and to handle data in streaming algorithms. Communication within a PP uses the more energy-efficient local buses. A single

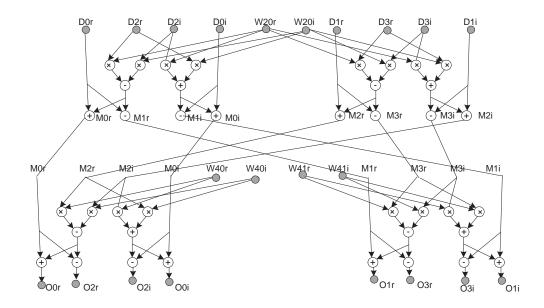

ALU has four 16-bit inputs. Each input has a private input register file that can store up to four operands. The input register file cannot be bypassed, i.e., an operand is always read from an input register. Input registers can be written by various sources via a flexible interconnect. An ALU has two 16-bit outputs, which are connected to the interconnect. The ALU is entirely combinatorial and consequently there are no pipeline registers within the ALU. The diagram of the Montium ALU in Figure 2.8 identifies two different levels in the ALU. Level 1 contains four function units. A function unit implements the general arithmetic and logic operations that are available in languages like C (except multiplication and division). Level 2 contains the Multiply-ACcumulate (MAC) unit and is optimized for algorithms such as FFT and FIR. Levels can be bypassed (in software) when they are not needed.

Neighboring ALUs can also communicate directly on level 2. The West-output of an ALU connects to the East-input of the ALU neighboring on the left (the West-output of the leftmost ALU is not connected and the East-input of the rightmost ALU is always zero). The 32-bit wide East-West connection makes it possible to accumulate the MAC result of the right neighbor to the multiplier result (note that this is also a MAC operation). This is particularly useful when performing a complex multiplication, or when adding up a large amount of numbers (up to 20 in one clock cycle). The East-West connection does not introduce a delay or pipeline, as it does not contain registers.

#### 2.5.6 Summary

Many coarse-grained reconfigurable architectures have been developed over the last 15 years. Although their details are different, they share several similarities:

- Coarse-grained reconfigurable architectures contain word-level function units, such as multipliers and arithmetic logic units.

- A major benefit of using word-level function units is a considerable reduction of configuration memory and configuration time.

- Reconfigurable communication networks are used in coarse-grained reconfigurable architectures. These networks support rich communication resources for efficient parallelism.

- Distributed storages (memories and registers) are used:

- to obtain a reasonable locality of reference

- to achieve a high memory bandwidth

- to relieve the von Neumann bottleneck

- The designs of coarse-grained reconfigurable architectures are kept simple to achieve high performance and low energy consumption. Automatic design or compiling tools are developed alongside the hardware designs, which map applications to the target architectures, using the particular features of the hardware.

#### 2.6 Conclusion

The existing computing architectures are divided into three groups: general purpose processers, application specific integrated circuits and reconfigurable architectures. General purpose processers are flexible, easy-to-use, but inefficient in performance and energy consumption. Application specific integrated circuits are the most efficient architectures, but inflexible. Reconfigurable architectures make a tradeoff between the efficiency and flexibility.

According to the width of the data-path, reconfigurable architectures are classified into two types: fine-grained and coarse-grained. In fine-grained reconfigurable architectures, the functionality of the hardware is specified at the bit level. In contrast, the data-path width in coarse-grained reconfigurable architectures is always more than one bit. This coarse granularity greatly reduces the delay, area, power and configuration time, compared with fine-grained architectures. However, these advantages come at the expense of flexibility compared with fine-grained architectures.

Compiler techniques are crucial for the future of coarse-grained reconfigurable architectures. Such tools allow application engineers to create algorithms without being an expert of the underlying hardware architectures. This reduces the design cycle and cost of new applications.

# Chapter 3

# The framework of a compiler for a coarse-grained reconfigurable architecture

This chapter<sup>1</sup> first gives an overview of the related work for mapping applications to coarse-grained reconfigurable architectures. Then we select the Montium tile processor as a sample architecture for our compiler. After that the challenges of the mapping problem for the Montium tile are discussed. Finally the framework of our mapping procedure is presented, which adopts a four-phase division: transformation, clustering, scheduling and allocation.

<sup>&</sup>lt;sup>1</sup>Parts of this chapter have been published in publication [2] [5].

#### 3.1 Introduction

In the process of designing a hardware architecture that is reconfigurable at run-time and is capable of performing many complex operations efficiently, the hardware engineers have come up with many trade-offs that often result in severe constraints being imposed on programming the processor. In this scenario, the compiler plays an important role of hiding the complex details of programming the embedded processor by allowing the users to write embedded applications in high level languages. The compiler is also responsible for ensuring that the embedded applications are translated to short and near-optimal code sequences. Only when the characteristics of a target reconfigurable architecture are used properly its strong points can be embodied during the application design. Otherwise the advantages of a system might become its disadvantages.

In the Gecko<sup>2</sup> project, a compiler is being developed to map applications to a coarse-grained reconfigurable architecture. The compiler is a high-level design entry tool which is capable of implementing programs written in a high-level language, such as C/C++ or Java, directly onto an array of reconfigurable hardware modules on a System-on-Chip (SoC).

#### 3.2 Overview of mapping methods

Many coarse-grained reconfigurable architectures are actually clustered microarchitectures. Compilers for coarse-grained reconfigurable architectures compilers could use some techniques that exist for clustered micro-architectures. Therefore, we first give an overview of some related design methods for clustered micro-architectures.

# 3.2.1 Mapping techniques for clustered micro-architectures

In a clustered micro-architecture, the register file and functional units are partitioned and grouped into clusters. Each cluster is connected to an interconnection network to allow communication with other clusters.

<sup>&</sup>lt;sup>2</sup>This research is supported by the Dutch organization for Scientific Research NWO, the Dutch Ministry of Economic Affaires and the technology foundation STW.

The problem of scheduling for clustered architectures consists of two main subproblems: (1) the assignment of data and operations to specific clusters; and (2) the coordination and scheduling of the moves of data between clusters.

In some of the previously published papers [24] [27] [49], cluster assignment and instruction scheduling are done sequentially. In other papers cluster assignment and scheduling are done in the reverse order. For example, Capitanio et al. considered the partitioning problems in [17] [18] for the Limited-Connectivity VLIW (LC-VLIW) architecture, where limited connectivity and register-to-register moves are allowed. According to [17] a partitioning algorithm is applied to a graph in order to divide the code into sub-streams that minimize a given cost function. Next inter-substream data movement operations are inserted and the code is recompacted.

In [68], the Unified Assign and Scheduling UAS algorithm is presented to perform clustering and scheduling on a clustered micro-architecture in a single step.

# 3.2.2 Compiling for coarse-grained reconfigurable architectures

Compiling applications written in a high-level language to coarse-grained reconfigurable platforms has been an active field of research in the recent past. The work in this domain is mostly highly dependent on the target architecture.

Typically, an application consists of computationally intensive 'kernels' that communicate with each other. Such an application can be described as a dataflow graph in which the nodes are 'kernels' or operations and the edges define the dependence between the nodes. The mapping work for the Pleiades SoC is done by directly mapping the dataflow graph of a kernel onto a set of satellite processors [1]. In this approach, each node or cluster of nodes in the dataflow graph corresponds to a satellite processor. Edges of the dataflow graph correspond to links in the communication network, connecting the satellite processors.

In Garp [41] [91], the reconfigurable hardware is an array of computing elements. The compiler draws heavily from techniques used in compilers for Very Long Instruction Word (VLIW) architectures to identify Instruction Level Parallelism (ILP) in the source program, and then schedules code

partitions for execution on the array of computing elements.

In CHIMAERA [94], the reconfigurable hardware is a collection of programmable logic blocks organized as interconnected rows. The focus of the compiler is to identify frequently executed instruction sequences and map them onto a Reconfigurable Functional Unit Operation (RFUOP) that will execute on the reconfigurable hardware.

PipeRench [12] [35] is a structure of configurable logic and storage elements interconnected by a network. The software development approach is to analyze the application's virtual pipeline, which is mapped onto physical pipe stages to maximize execution throughput. The compiler uses a greedy place and route algorithm to map these pipe stages onto the reconfigurable fabric.

The Reconfigurable Architecture Workstation (RAW) micro-architecture [90][6][58] comprises a set of inter-connected replicated tiles, each tile contains its own program and data memories, ALUs, registers, configurable logic and a programmable switch that can support both static and dynamic routing. The compiler partitions the program into multiple, coarse-grained parallel threads, each of which is then mapped onto a set of tiles.

The RaPiD architecture is a general coarse-grained reconfigurable architecture architecture with function units and buses. These are interconnected and controlled using a combination of static and dynamic control. The compilation techniques for RaPid are presented in [26].

Architecture for Dynamically Reconfigurable Embedded Systems (ADRES) is a template which couples a very-long instruction word (VLIW) processor and a coarse-grained array by providing two functional views on the same physical resources. DRESC is a compiler framework designed by the Interuniversity Microelectronics Center (IMEC) in Belgium for their architecture template ADRES [64].

The Morphosys architecture [81] consists of a general purpose processor core and an array of ALU-based reconfigurable processing elements. In their approach they use a language SA-C, an expression-oriented single assignment language. The paper [54] addresses the problem of compiling a program written in a high-level language, SA-C, to a coarse-grained reconfigurable architecture, Morphosys.

The Dynamically Reconfigurable ALU Array (DRAA) architecture [59][60] has some processing elements placed in a two dimensional array. Each processing element is a word-level reconfigurable function block. The processing elements communicate with each other by the interconnections. The spe-

cial requirement of DRAA to its compiler is that all element rows (columns) should have the same interconnection scheme. Therefore, the compiler of DRAA should exploit the regularity of an application algorithm.

Some research efforts [63], [74] have been focused on generic issues and problems in compilation like optimal code partitioning, and optimal scheduling of computation kernels for maximum throughput. While [74] proposes dynamic programming to generate an optimal kernel schedule, [63] proposes an exploration algorithm to produce the optimal linear schedule of kernels.

#### 3.2.3 Summary

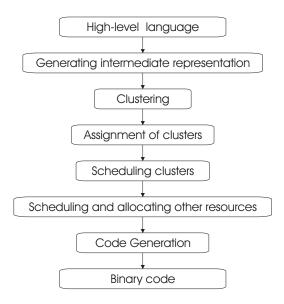

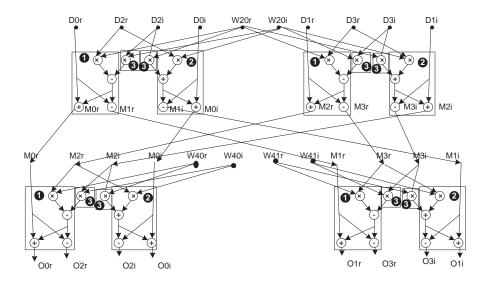

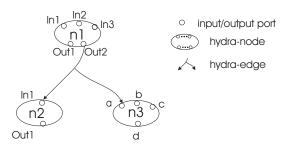

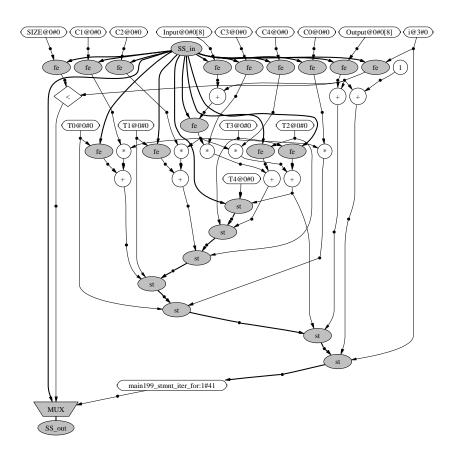

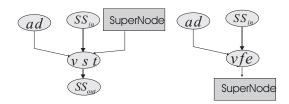

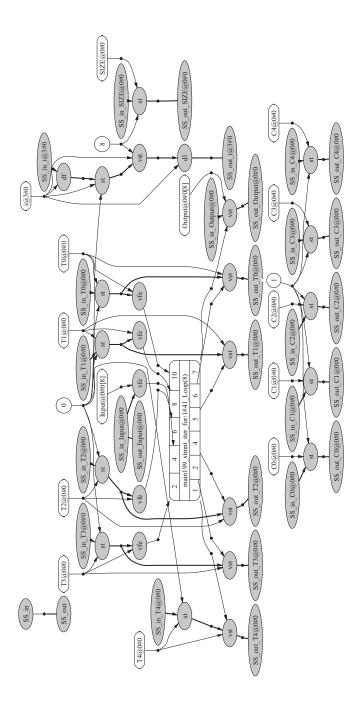

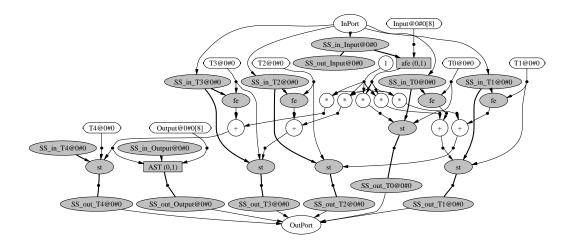

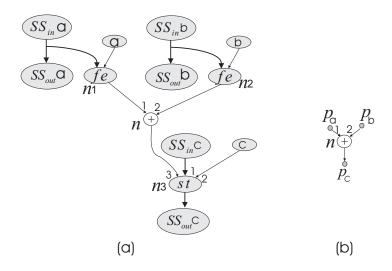

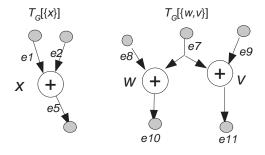

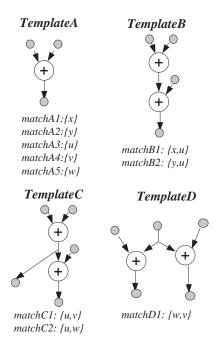

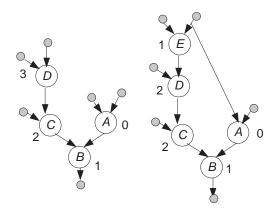

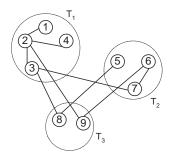

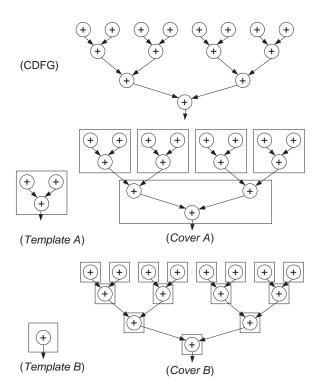

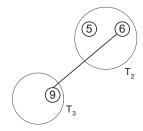

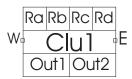

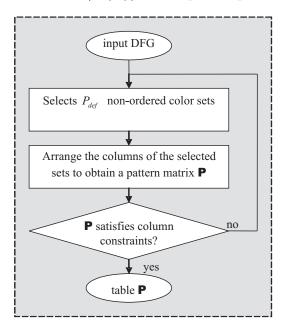

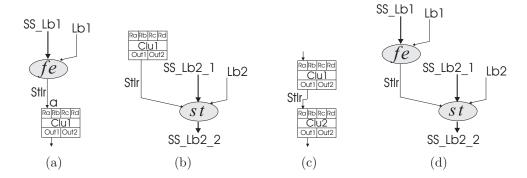

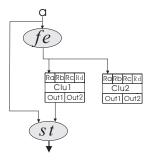

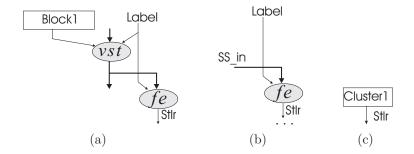

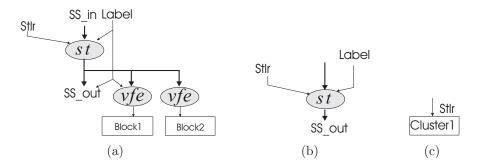

Figure 3.1: General structure of compilers for a coarse-grained reconfigurable architecture

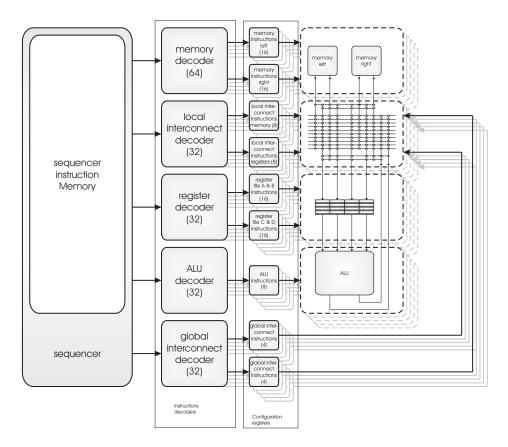

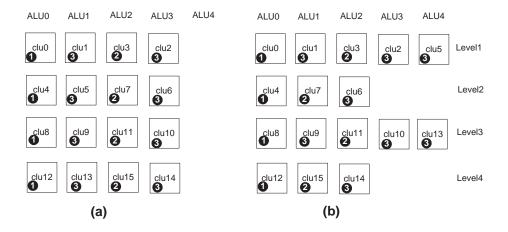

Compilers are usually highly dependent on the structure of the target architecture. As we discussed in Chapter 2, there are some similarities among all these architectures. Therefore, their compilers have some commonness as well. The general structure of a compiler can be presented by Figure 3.1. At the "Generating intermediate representation" phase, the initial application program, which is written in a high level language, will be translated into an intermediate representation. The intermediate representation is usually

convenient for parallelism extraction because most coarse-grained reconfigurable architectures have many parallel function units. When the function unit (or ALU) can execute more than one primary function, the "Clustering" phase is needed to combine the primary operations into clusters. The clusters are allocated to a function unit at the "Assignment of clusters" phase. And then the execution order of these clusters is scheduled at the "Scheduling of clusters" phase. After that, the communications are scheduled, and register and memory allocations are done at the "Scheduling and allocating other resources" phase. Finally the binary code is generated at the "Code generation" phase.

Not all compilers have the complete stream as described in Figure 3.1. For example, DIL is designed as the input language of the PipeRench [12] [35] compiler, so the "Generating intermediate representation" phase is not needed there. If the function units cannot run several primary functions in one clock cycle, the "Clustering" phase can also be skipped. For complex ALUs such as the ALU of the Montium tile processor (see Figure 2.8), the "Clustering" phase plays a very important role in reducing execution clock cycles. The "Assignment of clusters" and "Scheduling of clusters" are often combined [68]. The "Scheduling and allocating other resources" phase highly depends on target architectures, and different architectures have different constraints and requirements.

In our compiler we start from a high language such as C. The reason to choose the high-level language C is that the majority of DSP algorithms is specified in C or Matlab. The system designers often start with an executable C or Matlab reference specification, and the final implementation can be verified against this reference specification.

#### 3.3 A sample architecture

In Chapter 2, we saw that there are many coarse-grained architectures designed during the last 15 years. They are different in detail although they have some common features. To test the algorithms of our compiler, we choose the Montium tile processor as the sample target architecture. There are several reasons for that.

• Firstly, the Montium tile processor has similar features compared to most other coarse-grained reconfigurable architectures. The methodology used in a Montium compiler for taking care of those common

constraints can also be used in compilers for most other coarse-grained reconfigurable architectures.

- Secondly, in the Montium tile processor a hierarchy of small programmable decoders is used to reduce the control overhead significantly. This control system reduces the energy consumption considerably. We believe that this technique will be used more and more in future designs. However, this technique comes as a new requirement for the compiler, i.e., the number of distinct instructions should be as small as possible (more details can be found in Section 3.4.3). This requirement has never been studied before.

- Thirdly, it is believed that the architecture design and compiler design should be done simultaneously. The Montium tile processor has been designed in our group, therefore we have detailed knowledge of the architecture. We are even in the position to suggest changes in the architecture to simplify the compiler design.

# 3.4 Challenges of designing a Montium compiler

The Montium has been designed for very high speed and low-power applications, and therefore there are some special requirements to the Montium compiler. For example, the Montium allows a limited number of configurations. This limitation has never appeared in one of the previous architectures. New solutions must be found for the architectural concepts applied in the Montium design.

#### 3.4.1 Optimization goals

Before designing a good Montium mapping tool, we need to answer one question first: what does "good" mean? The answer goes back to the motivation of the Montium design – speed and energy-efficiency. That is to reduce the amount of clock cycles for the execution and to reduce the energy consumption of an application. The Montium architecture offers the following opportunities for these objectives.

• High speed through parallelism.

# CHAPTER 3: THE FRAMEWORK OF A COMPILER FOR A COARSE-GRAINED RECONFIGURABLE ARCHITECTURE

- One ALU can execute several primitive operations within one clock cycle.

- Five parallel ALUs can run at the same time.

- The crossbar and distributed storage places allow for parallel fetching and storing of data.

#### • Energy-efficiency through locality of reference.

- Using the data in a local register is more energy-efficient than using the data in a non-local register.

- Using the data in a local memory is more energy-efficient than using the data in a non-local memory.

- Using the data in a local register is more energy-efficient than using the data in a local memory.

A good compiler should find a mechanism to exploit the above mentioned opportunities given by the Montium architecture to generate a fast and low-power mapping. However, sometimes certain conflicts between the reduction of clock cycles and locality of reference may appear, i.e., the mapping scheme with locality of reference could take longer execution time. In that case, we choose a minimal number of clock cycles as a more important criterion mainly because the performance is a more important concern in most cases, and furthermore because more clock cycles definitely cost more energy.

#### 3.4.2 Constraints

Besides the above optimization objectives, the hardware of the Montium defines some constraints for the mapping problem. The constraints can be divided into two groups. One group refers to the constraints given by the number of resources such as number of memories, number of ALUs, etc, which are presented in Chapter 2. Another group is the limitation of configuration spaces. As a reconfigurable architecture, a Montium does not support as many different instructions as a general purpose processor does. The instructions in an application for a Montium should be as regular as possible. In other words, we like to have the same instruction being repeated for many times instead of having many different instructions being used once. The regularity is embodied by the limitations to the size of configuration spaces which will be explained in more detail in Section 3.4.3.